## **Laboratory 2**

(Due date: **002**: February 5<sup>th</sup>, **003**: February 6<sup>th</sup>)

## **OBJECTIVES**

- ✓ Implement a large combinational circuit using the Structural Description in VHDL.

- ✓ Introduce floating point and fixed point representations for VHDL implementation and Vivado simulation.

## VHDL CODING

✓ Refer to the <u>Tutorial: VHDL for FPGAs</u> for parametric code for: adder/subtractor and busmux.

## FIRST ACTIVITY: FLOATING POINT ADDER/SUBTRACTOR (100/100)

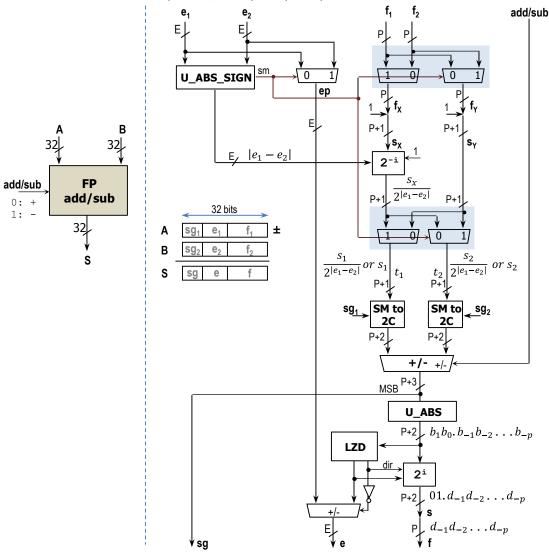

■ Implement the following single-precision (E=8, P=23), floating point adder/subtractor. The circuit only works for ordinary numbers generating ordinary numbers (e.g.: the cases  $S = A \pm B = 0$ , A = 0, or B = 0 are not considered by this circuit). The exponents in the circuit are biased exponents, so they always are positive numbers.

• **U\_ABS\_SIGN**: This circuit computes the absolute value of the difference of two unsigned numbers ( $e_1$  and  $e_2$ ). It also generates the signal sm.

$$e_1, e_2 \in [0, 2^E - 1] \rightarrow e_1 - e_2 \in [-(2^E - 1), 2^E - 1] \rightarrow |e_1 - e_2| \in [0, 2^E - 1]$$

. So,  $|e_1 - e_2|$  only needs  $E$  bits as an unsigned number.

$$e_1 \geq e_2 \rightarrow sm = 0, ep = e_1, f_x = f_2, f_y = f_1$$

$$e_1 < e_2 \rightarrow sm = 1, ep = e_2, f_x = f_1, f_y = f_2$$

| sm    | ep    | $\mathcal{S}_{\chi}$ | $s_y$         | $t_1$                       | $t_2$                       |

|-------|-------|----------------------|---------------|-----------------------------|-----------------------------|

| <br>0 | $e_1$ | $s_2 = 1.f_2$        | $s_1 = 1.f_1$ | $s_1$                       | $\frac{s_2}{2^{ e_1-e_2 }}$ |

| <br>1 | $e_2$ | $s_1 = 1.f_1$        | $s_2 = 1.f_2$ | $\frac{s_1}{2^{ e_1-e_2 }}$ | s <sub>2</sub>              |

$s_x$ : operand that gets divided by  $2^{|e_1-e_2|}$

- **Barrel shifter 2**-i: This circuit performs alignment of  $s_x$ , where we always shift to the right by  $|e_1 e_2|$  bits. Use the VHDL code mybarrelshift gen.vhd with dir='1' and SHIFTTYPE = "LOGICAL".

- SM to 2C: This block converts a number represented as a sign and magnitude into a 2C number. If sign is '0', then we append a 0 to the MSB. If the sign is '1', we get the negative number in 2C representation. This increases the bit-width to P + 2 bits.

- **Main adder/subtractor**: This circuit operates in 2C arithmetic. Note that it is implied that we need to sign-extend the (P+2)-bit operands to P+3 bits. Input operands  $\in [-2^{P+1}+1,2^{P+1}-1]$ , Output result  $\in [-2^{P+2}+2,2^{P+2}-2]$ .

- **U\_ABS block**: It takes the absolute value of a number represented in 2C arithmetic. The output is provided as an unsigned number. The absolute value  $\in [0, 2^{P+2} 2]$ , this only requires P + 2 bits in unsigned representation.

| result | output                     | sign | Actions                                                                                                                               |

|--------|----------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------|

| [0,p]  | <i>sh</i> ∈ [0, <i>p</i> ] | 0    | The barrel shifter needs to shift to the left by $sh$ bits. Exponent adder/subtractor needs to subtract $sh$ from the exponent $ep$ . |

| -1     | sh = 1                     | 1    | The barrel shifter needs to shift to the right by 1 bit. Exponent adder/subtractor needs to add 1 to the exponent $ep$ .              |

- **Exponent adder/subtractor**: The figure is not detailed. This circuit operates in 2C arithmetic; as the input operands are unsigned, we zero-extend to E+1 bits. Note that for ordinary numbers,  $ep ∈ [1, 2^E 2]$ . The (E+1)-bit result (biased exponent) cannot be negative: at most, we subtract P from ep, or add 1. Thus, we use the unsigned portion: E bits (LSBs).

- Barrel shifter 2<sup>i</sup>: It performs normalization of the final summation. We shift to the left (from 0 to P bits) or to the right (1 bit). Use the VHDL code mybarrelshift\_GEN.vhd with SHIFTTYPE="LOGICAL" (unsigned input), dir=sign(LZD).

- VIVADO DESIGN FLOW FOR FPGAs NEXYS A7-50T

- ✓ Create a new Vivado Project. Select the **XC7A50T-1CSG324 Artix-7 FPGA** device.

- ✓ Write the VHDL code for the 32-bit floating point adder subtractor. Utilize the Structural Description: create a separate file for the components (2-to-1 bus MUX, SM to 2C, U\_ABS, LZD, Barrel shifter, adder/subtractor, U\_ABS\_SIGN), and the top file (where you will interconnect all the components).

- ✓ Write the VHDL testbench to test the following cases:

| 60A10000 | + | C2F97000 | = | 60A10000 |

|----------|---|----------|---|----------|

| 40B00000 | + | C2FA8000 | = | C2EF8000 |

| 42FA8000 | + | C0E00000 | = | 42EC8000 |

| 10DAD000 | _ | 90FAD000 | = | 116AD000 |

| 3DE38866 | _ | B300D959 | = | 3DE3886A |

| 60A10000 | _ | 60A1F000 | = | DCF00000 |

- ✓ Perform <u>Functional Simulation</u> and <u>Timing Simulation</u> of your design. **Demonstrate this to your TA**.

Note that when testing, it might be very useful to represent the inputs and output in single floating point precision. Or we might also want to represent the intermediate signals not only as integer numbers but also as fixed point numbers. You can use the Radix → Real Settings in Vivado simulator window to do so.

- Submit (<u>as a .zip file</u>) all the generated files: VHDL code files and VHDL testbench to Moodle (an assignment will be created).

DO NOT submit the whole Vivado Project.

| TA signature: | Date: |  |

|---------------|-------|--|

|               |       |  |